國產(chǎn)EDA扎堆亮相,異構(gòu)集成刷屏熱議 世界半導(dǎo)體大會的集成電路設(shè)計(jì)風(fēng)向標(biāo)

世界半導(dǎo)體大會的集成電路設(shè)計(jì)專題論壇成為了全球產(chǎn)業(yè)與技術(shù)關(guān)注的焦點(diǎn)。兩大核心趨勢——國產(chǎn)EDA(電子設(shè)計(jì)自動化)工具的集中突破與異構(gòu)集成的技術(shù)深化,構(gòu)成了本次盛會的技術(shù)主旋律,深刻揭示了后摩爾時代芯片設(shè)計(jì)領(lǐng)域的關(guān)鍵演進(jìn)路徑。

國產(chǎn)EDA:從“點(diǎn)工具”到“全流程”,生態(tài)突圍進(jìn)行時

本屆大會上,多家國內(nèi)領(lǐng)先的EDA企業(yè)集中展示了最新研發(fā)成果,覆蓋了從模擬電路設(shè)計(jì)、數(shù)字前端到后端物理實(shí)現(xiàn)、封裝仿真乃至芯片制造良率提升等多個環(huán)節(jié)。與以往在個別“點(diǎn)工具”上取得突破不同,當(dāng)前的展示更強(qiáng)調(diào)全流程解決方案的整合能力與對先進(jìn)工藝節(jié)點(diǎn)的支持。

核心亮點(diǎn)包括:

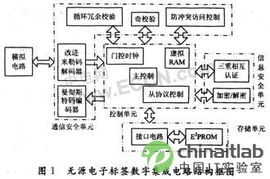

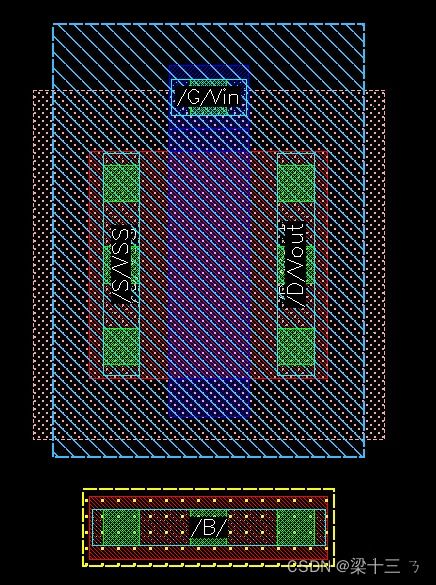

1. 全流程工具鏈雛形顯現(xiàn): 部分國產(chǎn)EDA平臺已能夠支撐特定領(lǐng)域的完整設(shè)計(jì)流程,例如在模擬/數(shù)模混合電路設(shè)計(jì)或特定工藝的物理設(shè)計(jì)方面,提供了從前端設(shè)計(jì)、仿真驗(yàn)證到版圖生成的一體化工具集,顯著降低了設(shè)計(jì)門檻和工具切換成本。

2. 與先進(jìn)工藝和封裝協(xié)同: 新一代工具加強(qiáng)了對FinFET等先進(jìn)工藝的適配,并開始深度集成面向Chiplet(芯粒)和異構(gòu)集成的設(shè)計(jì)、仿真與驗(yàn)證模塊,體現(xiàn)了從跟隨到面向未來需求的轉(zhuǎn)變。

3. 產(chǎn)學(xué)研用協(xié)同深化: 大會期間,多家EDA公司與頭部芯片設(shè)計(jì)企業(yè)、晶圓廠及高校簽署了深度合作協(xié)議,旨在通過實(shí)際項(xiàng)目打磨工具,加速迭代,共同構(gòu)建更健壯的國產(chǎn)EDA應(yīng)用生態(tài)。

業(yè)界共識認(rèn)為,國產(chǎn)EDA正從“可用”向“好用、易用”階段邁進(jìn),但挑戰(zhàn)依然存在,包括在超大規(guī)模數(shù)字電路設(shè)計(jì)、尖端工藝PDK(工藝設(shè)計(jì)套件)的完整支持以及與全球最復(fù)雜IP生態(tài)的深度融合等方面,仍需持續(xù)攻堅(jiān)。

異構(gòu)集成:超越摩爾定律的“C位”技術(shù)

如果說EDA是設(shè)計(jì)之“筆”,那么異構(gòu)集成則代表了設(shè)計(jì)思想之“魂”。本次大會上,異構(gòu)集成技術(shù)占據(jù)了技術(shù)討論的絕對“C位”,成為應(yīng)對算力需求爆炸、功能多樣化與能效挑戰(zhàn)的核心答案。

討論焦點(diǎn)集中在以下幾個方面:

1. Chiplet(芯粒)互連與標(biāo)準(zhǔn): 如何實(shí)現(xiàn)不同工藝節(jié)點(diǎn)、不同功能、不同來源(甚至不同廠商)的Chiplet之間的高速、高帶寬、低功耗互連,是技術(shù)關(guān)鍵。大會深入探討了UCIe(通用芯粒互連技術(shù))等新興開放標(biāo)準(zhǔn)的進(jìn)展、挑戰(zhàn)與生態(tài)建設(shè)路徑。國內(nèi)產(chǎn)業(yè)界也在積極推動相關(guān)標(biāo)準(zhǔn)的研究與制定。

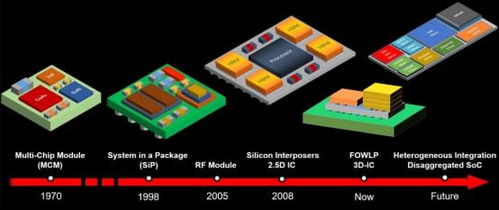

2. 先進(jìn)封裝技術(shù)驅(qū)動: 異構(gòu)集成的實(shí)現(xiàn)高度依賴于2.5D/3D封裝、硅通孔(TSV)、扇出型(Fan-Out)等先進(jìn)封裝技術(shù)。封裝廠與設(shè)計(jì)公司的協(xié)同設(shè)計(jì)(Co-Design)成為必然趨勢,EDA工具需要為此提供從架構(gòu)探索、物理實(shí)現(xiàn)到熱、應(yīng)力、信號完整性分析的全面支持。

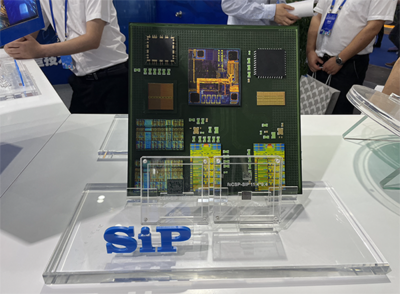

3. 系統(tǒng)級架構(gòu)創(chuàng)新: 異構(gòu)集成不僅僅是物理上的堆疊,更是系統(tǒng)架構(gòu)的革新。設(shè)計(jì)思路從單一SoC(系統(tǒng)級芯片)轉(zhuǎn)向基于芯粒的“樂高式”系統(tǒng)級封裝(SiP),如何在不同計(jì)算單元(CPU、GPU、NPU、FPGA等)之間實(shí)現(xiàn)高效的存算一體、數(shù)據(jù)調(diào)度與任務(wù)分配,是提升整體系統(tǒng)性能的關(guān)鍵。

4. 設(shè)計(jì)方法論變革: 傳統(tǒng)的芯片設(shè)計(jì)流程正被重構(gòu)。系統(tǒng)架構(gòu)師、芯片設(shè)計(jì)師、封裝工程師、軟件開發(fā)者需要更早、更緊密地協(xié)作。新的設(shè)計(jì)工具鏈和驗(yàn)證方法學(xué)(如芯片-封裝-系統(tǒng)協(xié)同仿真)亟待完善。

融合與展望:設(shè)計(jì)、工具與生態(tài)的共舞

世界半導(dǎo)體大會清晰地表明,集成電路設(shè)計(jì)的是國產(chǎn)EDA工具的自主創(chuàng)新與異構(gòu)集成的系統(tǒng)級突破兩條主線深度融合、相互促進(jìn)的進(jìn)程。

- EDA工具必須擁抱異構(gòu)集成的復(fù)雜性,發(fā)展出能夠處理多物理域、多尺度、多工藝協(xié)同設(shè)計(jì)與分析的下一代平臺。

- 異構(gòu)集成技術(shù)的廣泛應(yīng)用與成本降低,反過來也離不開強(qiáng)大、靈活且成本可控的EDA工具支持。

- 開放合作的產(chǎn)業(yè)生態(tài)是成敗的關(guān)鍵。從芯粒接口標(biāo)準(zhǔn)、IP復(fù)用、到設(shè)計(jì)與制造服務(wù)的協(xié)同,構(gòu)建一個全球或區(qū)域性的、基于開放標(biāo)準(zhǔn)的異構(gòu)集成生態(tài)系統(tǒng),將是整個產(chǎn)業(yè)面臨的共同課題。

結(jié)論: 本屆世界半導(dǎo)體大會為集成電路設(shè)計(jì)領(lǐng)域描繪了一幅清晰的圖景:在后摩爾時代,通過國產(chǎn)EDA的全流程攻堅(jiān)與異構(gòu)集成的系統(tǒng)級創(chuàng)新“雙輪驅(qū)動”,中國集成電路產(chǎn)業(yè)正致力于在基礎(chǔ)工具和前沿設(shè)計(jì)方法學(xué)上構(gòu)建核心競爭力,以期在全球半導(dǎo)體產(chǎn)業(yè)的新一輪格局重塑中占據(jù)更主動的位置。前路挑戰(zhàn)艱巨,但方向已然明確,步伐正在加速。

如若轉(zhuǎn)載,請注明出處:http://www.pai3.cn/product/59.html

更新時間:2026-01-22 00:07:59