從0開(kāi)始的Cadence Virtuoso模擬集成電路設(shè)計(jì)學(xué)習(xí)筆記(三) 反相器版圖繪制與后仿真驗(yàn)證

在完成了反相器的電路設(shè)計(jì)與前仿真之后,我們正式進(jìn)入模擬集成電路設(shè)計(jì)的核心物理實(shí)現(xiàn)環(huán)節(jié)——版圖(Layout)設(shè)計(jì),并對(duì)其進(jìn)行后仿真驗(yàn)證。本筆記將詳細(xì)記錄在Cadence Virtuoso環(huán)境中,一個(gè)CMOS反相器從版圖繪制到物理驗(yàn)證、提取寄生參數(shù),最終完成后仿真的完整流程。

一、 版圖設(shè)計(jì):將電路圖轉(zhuǎn)化為物理圖形

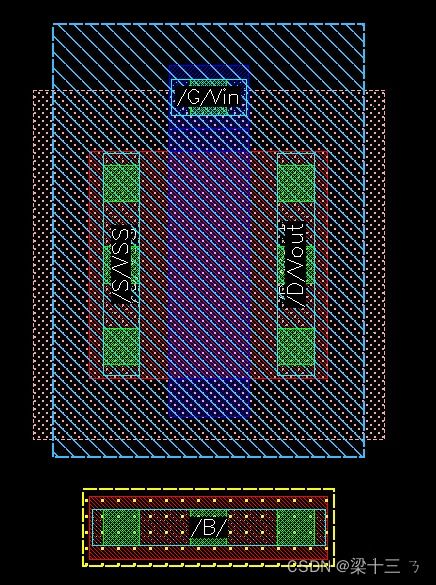

版圖是電路的物理描述,是芯片制造的藍(lán)圖。在Virtuoso Layout Editor中,我們開(kāi)始繪制反相器的版圖。

- 創(chuàng)建與設(shè)置:在Library Manager中,為反相器電路圖(schematic)創(chuàng)建對(duì)應(yīng)的版圖視圖(Layout)。首先設(shè)置正確的工藝設(shè)計(jì)規(guī)則文件(Display.drf或TF文件),這決定了不同圖層(如nwell, pplus, poly, metal1等)的顏色與填充樣式。

- 核心器件繪制:

- PMOS與NMOS晶體管:使用

Instance工具調(diào)用PDK(工藝設(shè)計(jì)套件)中的標(biāo)準(zhǔn)MOS管版圖單元,或根據(jù)W/L參數(shù)手動(dòng)繪制。關(guān)鍵步驟包括:繪制有源區(qū)(Active),多晶硅柵(Poly),以及注入層(nplus/pplus)形成源漏區(qū)。PMOS管需要放置于N阱(Nwell)中。務(wù)必保證柵極對(duì)齊,這是反相器正常工作的基礎(chǔ)。

- 連接:使用金屬層(如Metal1)連接PMOS的漏極與NMOS的漏極作為輸出端;連接PMOS的源極到VDD(電源,通常用高層金屬如Metal2);連接NMOS的源極到VSS(地,用Metal1或Metal2)。輸入端(柵極)也用Metal1連接至多晶硅。

- 遵循設(shè)計(jì)規(guī)則:繪制過(guò)程中,必須嚴(yán)格遵守DRC(設(shè)計(jì)規(guī)則檢查)規(guī)則,包括最小線寬、最小間距、包圍、延伸等。這是確保芯片可制造、良率高的生命線。

- 添加引腳與標(biāo)簽:使用

Pin工具創(chuàng)建輸入(IN)、輸出(OUT)、電源(VDD)和地(VSS)的物理引腳,并為其打上文本標(biāo)簽(Label),標(biāo)簽名稱(chēng)必須與電路圖中的網(wǎng)絡(luò)名一致,以便于后續(xù)的LVS比對(duì)。

二、 物理驗(yàn)證:確保版圖正確無(wú)誤

版圖繪制完成后,必須通過(guò)嚴(yán)格的物理驗(yàn)證。

- DRC(設(shè)計(jì)規(guī)則檢查):運(yùn)行DRC,檢查版圖是否符合工藝廠的所有幾何規(guī)則。Virtuoso通常集成Calibre或Assura等工具。必須解決所有DRC錯(cuò)誤(Error)和警告(Warning),直至報(bào)告“clean”。

- LVS(版圖與電路圖一致性檢查):這是至關(guān)重要的一步,用于驗(yàn)證繪制的版圖是否與原始電路圖在電氣連接上完全一致。運(yùn)行LVS工具,它會(huì)比較網(wǎng)表:

- 提取:從版圖中提取出包含所有晶體管和連接的電路網(wǎng)表。

- 比對(duì):將此網(wǎng)表與反相器電路圖生成的網(wǎng)表進(jìn)行比對(duì)。

- 成功標(biāo)志是看到“NETS ARE EQUAL”和“DEVICES ARE EQUAL”的提示,表明版圖與原理圖匹配。

三、 寄生參數(shù)提取與后仿真

通過(guò)LVS后,版圖在邏輯上已正確。但真實(shí)的版圖存在寄生電阻(R)、寄生電容(C),甚至寄生電感(在高速設(shè)計(jì)中)。這些寄生效應(yīng)會(huì)顯著影響電路性能(如速度、功耗),因此必須進(jìn)行后仿真(Post-layout Simulation)。

- 提取寄生參數(shù):使用RCX(寄生參數(shù)提取)工具(如Quantus、Calibre xRC等)對(duì)通過(guò)驗(yàn)證的版圖進(jìn)行提取。工具會(huì)根據(jù)金屬線的尺寸、間距、層間介質(zhì)等信息,生成一個(gè)包含所有寄生R和C的詳細(xì)網(wǎng)表(通常為SPICE格式)。

- 設(shè)置后仿真:

- 在Virtuoso ADE Explorer或ADE Assembler中,建立一個(gè)新的仿真環(huán)境。

- 在

Setup->Environment中,將Simulation標(biāo)簽下的Switch View List設(shè)置為包含extracted視圖(即寄生參數(shù)提取后生成的視圖),并確保其優(yōu)先級(jí)高于schematic視圖。這樣仿真器就會(huì)調(diào)用包含寄生信息的網(wǎng)表進(jìn)行仿真。

- 運(yùn)行與結(jié)果分析:

- 施加與前仿真相同的測(cè)試條件(如輸入脈沖信號(hào)、電源電壓、負(fù)載電容等)。

- 運(yùn)行瞬態(tài)分析(tran),觀察輸入輸出波形。

- 關(guān)鍵對(duì)比:將后仿真結(jié)果與前仿真結(jié)果疊加對(duì)比。通常會(huì)觀察到:

- 延遲增加:由于寄生RC的充放電,輸出信號(hào)的上升/下降時(shí)間變長(zhǎng),傳播延遲增加。

- 波形變緩:邊沿不再像前仿真那樣陡峭。

- 功耗可能微變:由于額外的寄生電容充放電,動(dòng)態(tài)功耗可能略有上升。

四、 迭代與優(yōu)化

如果后仿真性能(如延遲、功耗)不滿足設(shè)計(jì)指標(biāo),則需要返回修改版圖。常見(jiàn)的優(yōu)化手段包括:

優(yōu)化走線,縮短關(guān)鍵路徑(如輸出節(jié)點(diǎn))的金屬線長(zhǎng)度以減少寄生電阻和電容。

使用更寬的金屬線(在DRC允許范圍內(nèi))以減少電阻。

* 重新規(guī)劃器件布局,減少互連距離。

修改后,必須重新進(jìn)行DRC、LVS和寄生參數(shù)提取,然后再次后仿真,直至性能達(dá)標(biāo)。

###

從電路圖(Schematic)到版圖(Layout),再到后仿真(Post-sim),是模擬IC設(shè)計(jì)從“理想”走向“現(xiàn)實(shí)”的必經(jīng)之路。反相器作為最基本的單元,其流程清晰地展現(xiàn)了這一核心循環(huán):設(shè)計(jì) -> 物理實(shí)現(xiàn) -> 驗(yàn)證(DRC/LVS)-> 評(píng)估性能(后仿真)-> 迭代優(yōu)化。熟練掌握這一流程,是后續(xù)設(shè)計(jì)更復(fù)雜模擬電路(如放大器、比較器、PLL)的堅(jiān)實(shí)基礎(chǔ)。版圖設(shè)計(jì)不僅要求電氣正確,更是一門(mén)追求性能、面積與可靠性平衡的藝術(shù)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.pai3.cn/product/66.html

更新時(shí)間:2026-01-22 13:00:42